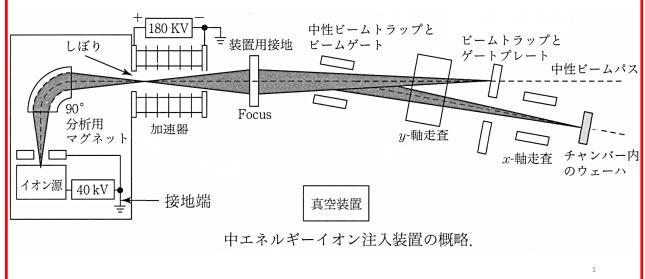

### 前回の復習: イオン注入法:

不純物をイオン化して、数~数百kVで加速して基板に打ち込み不純物ドーピングを行う。熱拡散法よりも低温で不純物拡散が出来るのでフォトレジストがマスクとしてそのまま使える。また、広範囲で精度良くドープ量を変えられ、マスク下への拡散も少ない。

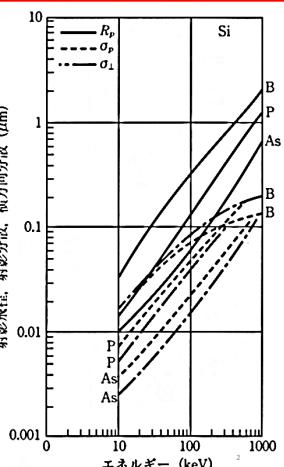

### 前回の復習: イオンの分布:

不純物イオンは、原子核や電子と繰り返し衝突して深さ $R_p$ (飛影距離)で止まる。その時のイオン分布 $n(x)$ は、 $n(x) =$

$$\frac{Q_s}{\sqrt{2\pi}\sigma_p} \exp\left\{-\frac{(x-R_p)^2}{2\sigma_p^2}\right\}$$

(10.1)となる。打ち込まれた不純物イオンは、横(表面平行)方向にも分散 $\sigma_{\perp}^2$ で広がるが、熱拡散法での横方向の広がりよりは小さい。また、射影飛程 $R_p$ は注入イオンエネルギーに依存している

### 前回の復習: イオン注入後のアニール: バッチ式電気炉と瞬時ランプ(RTP: Rapid Thermal Processing)による方法がある。

| 要素       | 電気炉     | RTP      |

|----------|---------|----------|

| プロセス     | バッチ     | 1枚ウェーハ   |

| 炉        | ホットウォール | コールドウォール |

| 昇温速度     | 低       | 高        |

| サイクル時間   | 高       | 低        |

| 温度モニター   | 炉       | ウェーハ     |

| 熱経費      | 高       | 低        |

| パーティクル問題 | 有       | 少        |

| 均一性と再現性  | 高       | 低        |

| スループット   | 高       | 低        |

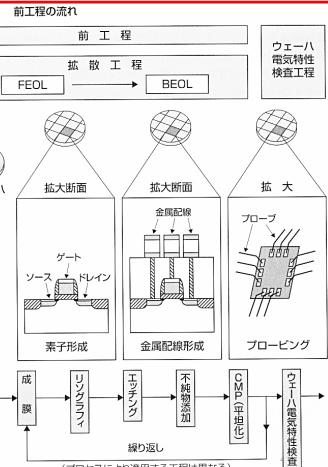

### 前工程: 集積回路の製造工程には、前工程と後工程がある。

これまでに学習した成膜やフォトリソグラフィーやエッ칭や不純物ドーピング等のSiウェハー上に電子回路を作り込むための製造工程は、すべて前工程にあたる。

また、前工程の中でも素子形成工程をFront End Of Line、配線形成工程をBack End Of Lineという。前回の復習:

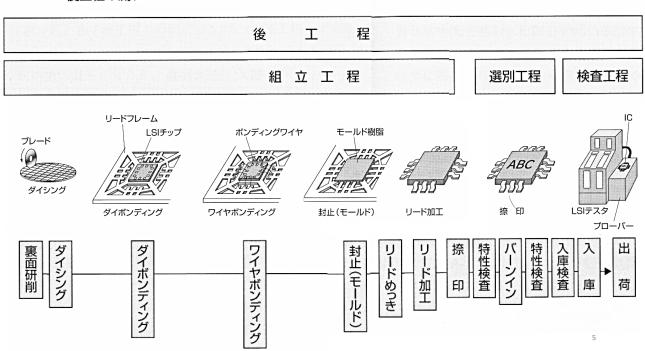

### 後工程:

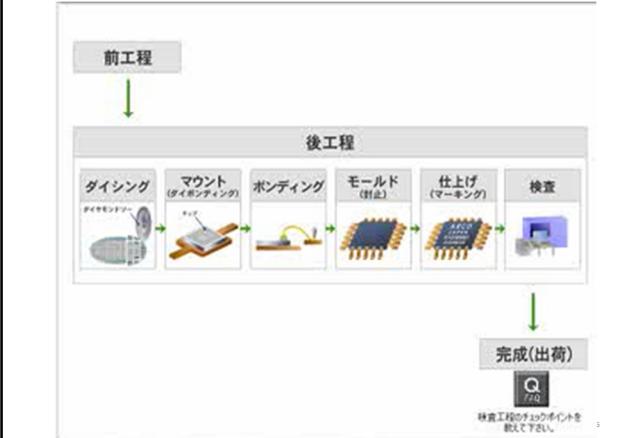

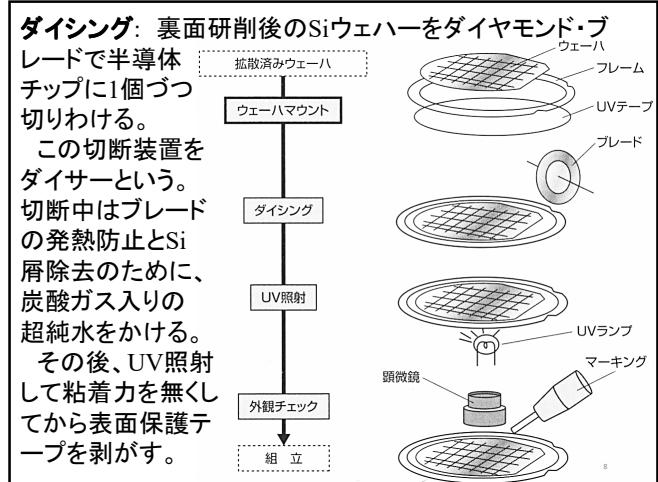

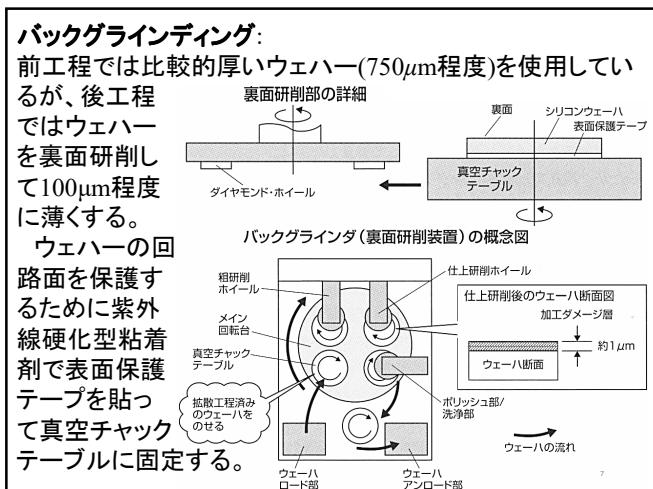

前工程でSiウェハー上に電子回路を製造した後に、後工程で一個づつの製品に加工する。

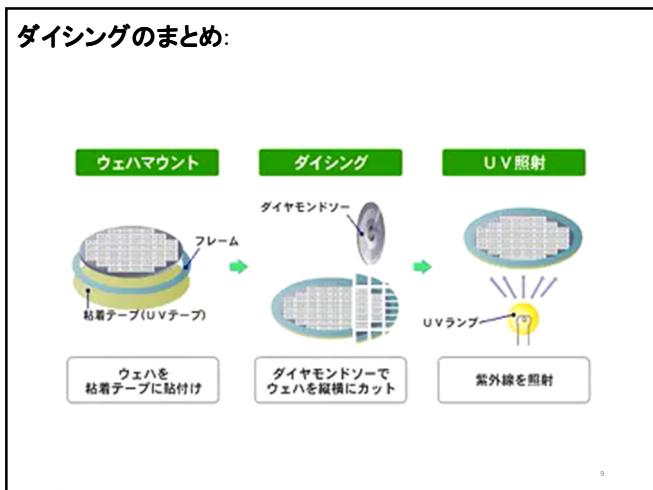

後工程の流れ

### 後工程の概要:

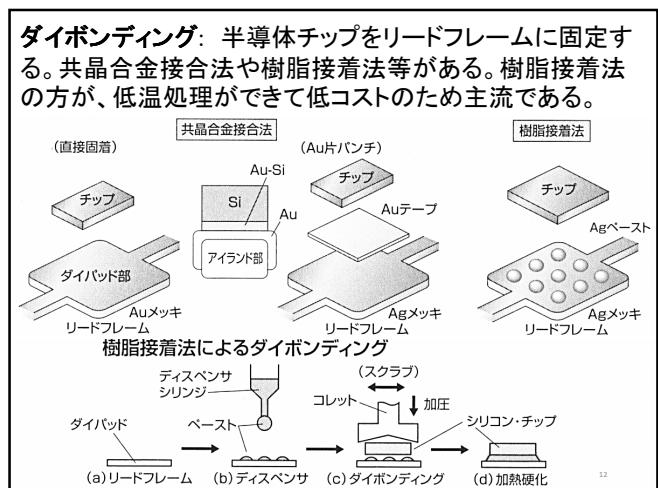

## 樹脂マウント法:

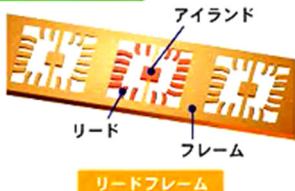

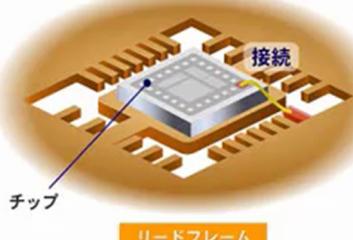

**マウント** = ダイポンディング

チップをリードフレーム枠に貼り付ける

### 樹脂マウント法

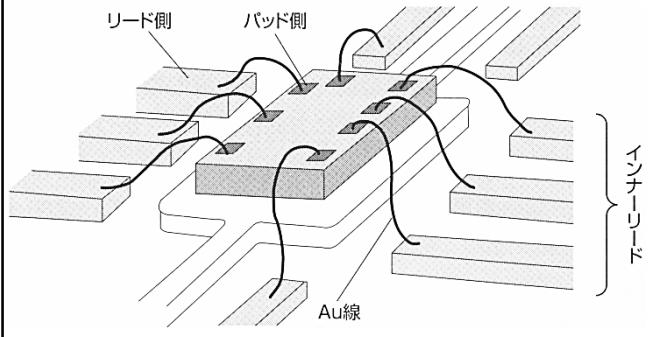

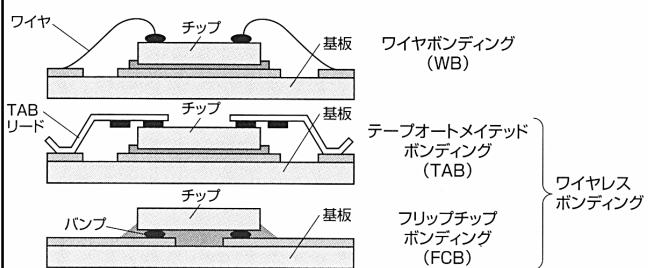

**配線の接続:** 半導体チップの電極パッドとリードフレームのインナーリード間を配線する。配線方法には、ワイヤボンディング(Au線のボールボンディング法とAl線のウェッジボンディング法)とワイヤレスボンディング法がある。

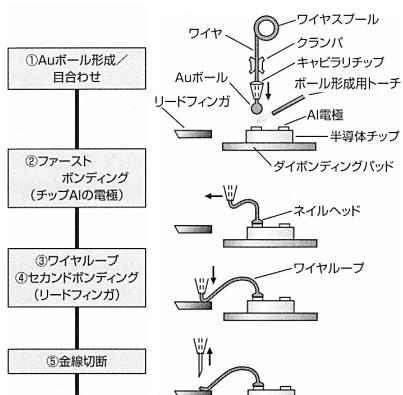

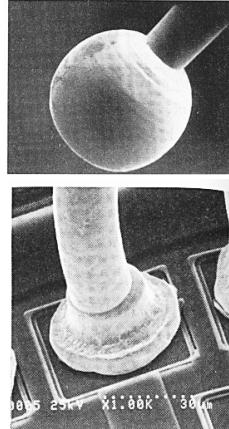

## ボールボンディング法: 直径数十μm程度のAu線を使う。

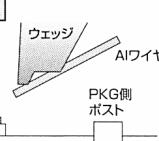

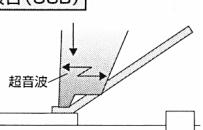

## ウェッジボンディング法: アルミ細線で配線する。

(AIワイヤ方式、超音波方式、ワイヤ方向性有り)

### (a) 位置合わせ

### (b) 接合 (USB)

| 項目          | ボールボンディング方式                                | ウェッジボンディング方式                            |

|-------------|--------------------------------------------|-----------------------------------------|

| ワイヤ材料       | Au 99.99%~50μmφ                            | Al - 1% Si~50μmφ                        |

| 電極          | チップ側: Al, 1 μmt<br>フレーム側: Au or Ag 1~3 μmt | チップ側: Al, 1 μmt<br>PKG側: Al or Ag 1 μmt |

| ボンディングタイプ   | チップ側: ボールボンディング<br>フレーム側: ウェッジボンディング       | 両側ともにウェッジボンディング                         |

| ボンディングエネルギー | 熱圧着(熱板) or 超音波併用熱圧着 (NTC) (UNTC)           | 超音波振動 (US)                              |

| ボンディング温度    | 280 ~ 350°C                                | 常温                                      |

## ボールボンディング法のまとめ:

### ボンディング

作業を行う装置: ボンダー

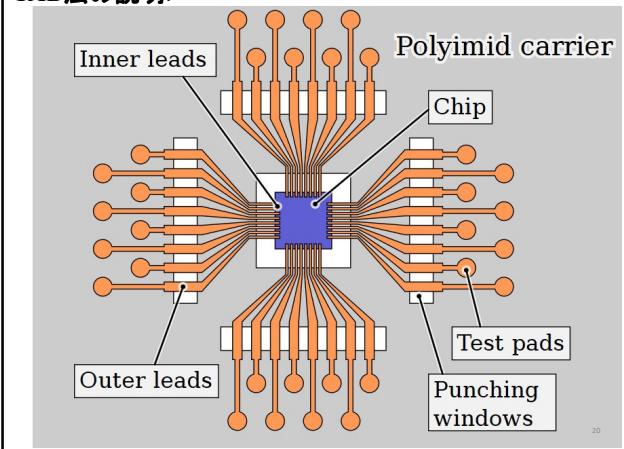

**ワイヤレスボンディング:** 金属細線を使わずに配線する。テープ・オートメイティッド・ボンディング(TAB)法とフリップチップ・ボンディング(FCB)法がある。両方法とも接続端子間隔を小さくして、端子数を増やすことができる。

### チップとパッケージ基板の接続方法

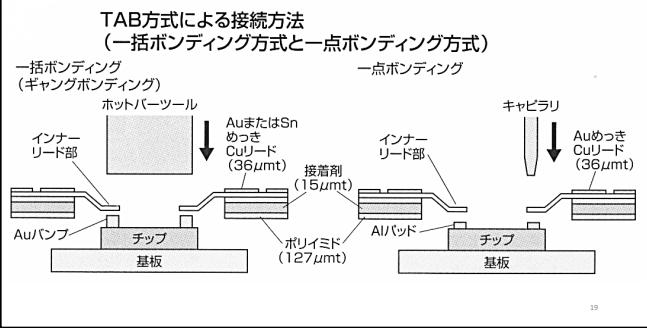

**TAB法:** 金属細線の代わりに複数のAuめっきしたリード線が組み込まれた樹脂フィルムテープを使う。半導体チップのAIパッド上にAuバンプを作り、そのAuバンプにリード線を熱圧着する。

### TAB法の説明:

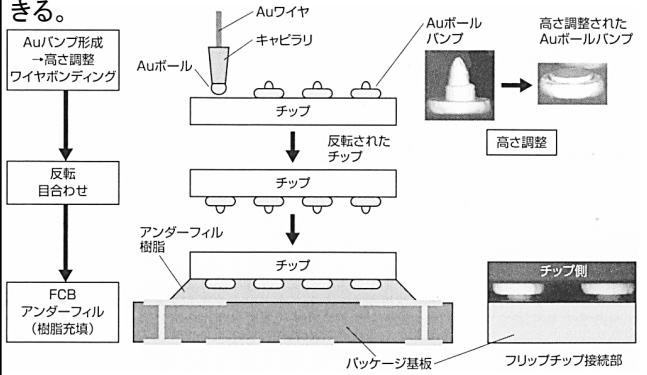

**FCB法:** パッド上にAuバンプを形成したチップを裏返して、パッケージの配線と接着する。接続配線長が短く、チップの全面に端子を作れるので、端子数を大幅に増やすことができる。

### フリップチップボンダー装置:

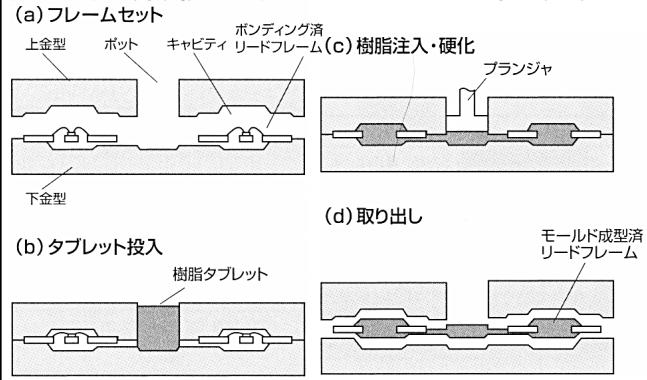

**樹脂封止:** 半導体チップを外部環境から保護するためにトランスマーモールド法で樹脂封止する。他にも、ガラス溶融封止、金属溶接封止、セラミックパッケージ等もある。

### トランスマーモールド法:

#### モールド

パッケージや封止材で密封する

トランスマーモールド法 安価で量産性に優れている

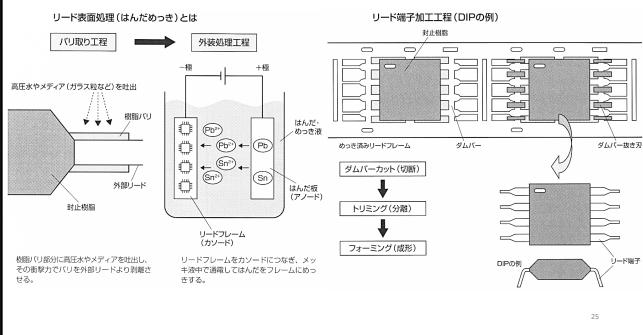

## パッケージの端子加工:

樹脂パリを取り、ハンダを電解メッキして、リードフレームからプレス切断機でICを1個づつ切り離して(トリミング)、リード端子を曲げて成形する。

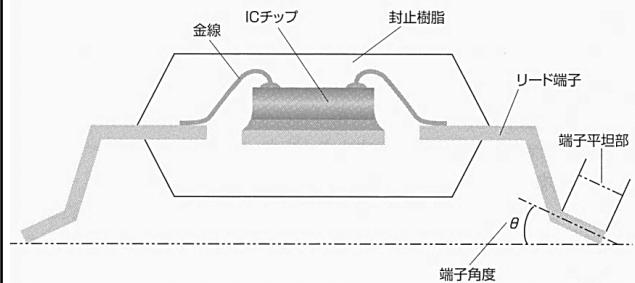

## 一般的なICの透視図:

ガルウイング型パッケージのリード端子平坦性とリード先端角度

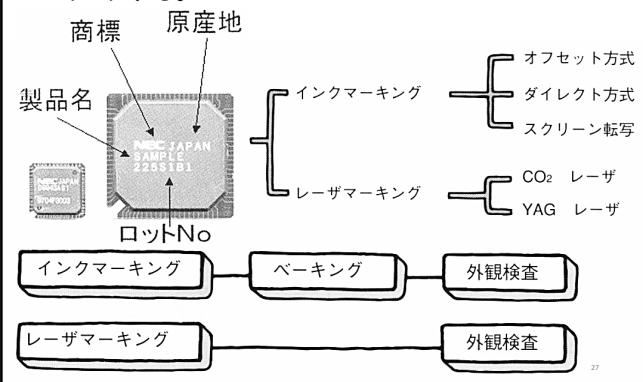

**マーキング:** 製造メーカー名、製品名、原産地、ロットNo等を、インクによる印刷方式かレーザー光線による印字方式でマーキングする。

## マーキングのまとめ:

捺印記号 製品を識別するマーク

トレーサビリティ 製品の製造履歴が確認できる

原因究明や迅速な対策・改善が可能

- ・社名

- ・組立原産地国名

- ・製品名

- ・製造ロット番号

- ・その他の管理番号

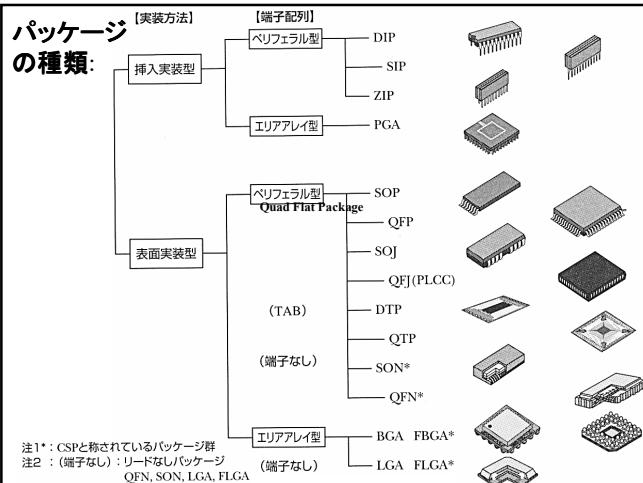

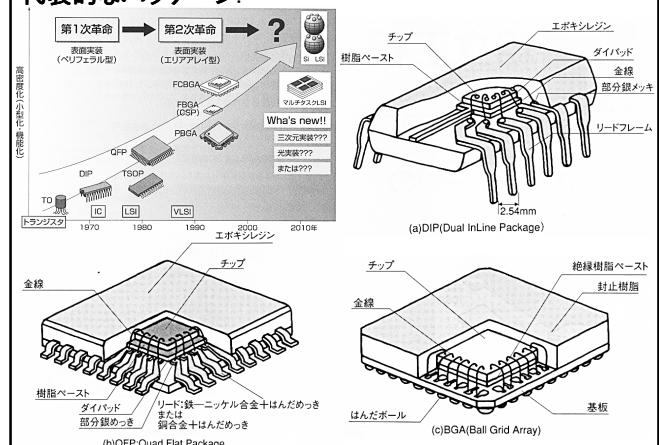

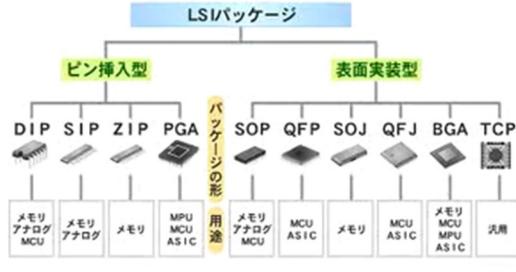

## パッケージの種類:

## 代表的なパッケージ:

## パッケージのまとめ:

### パッケージの目的

- 半導体チップを保護

- + 軽薄短小の要求に応えて

多種多様な種類が開発されている

## Multi-Chip Module:

複数のICチップをパッケージに封止して一つのICにする。プリント基板を通さずにパッケージ内でインターポーラーを介して配線することで信号の伝達遅れを最小限にして、システムを高速化・コンパクト化できる。

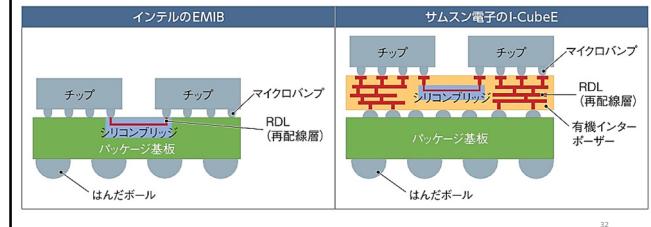

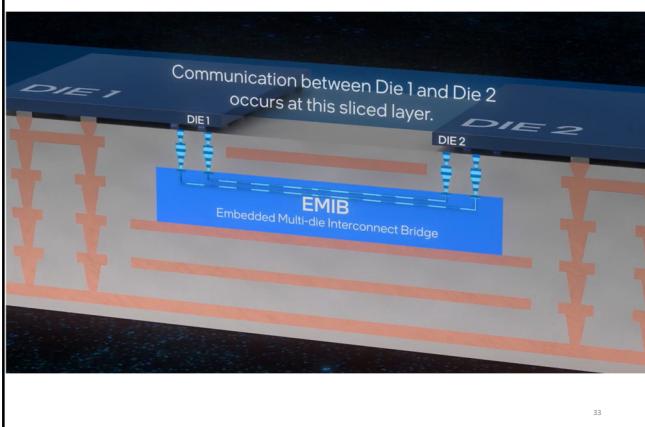

### Embedded Multi-die Interconnect Bridge (EMIB)

## Intel EMIB:

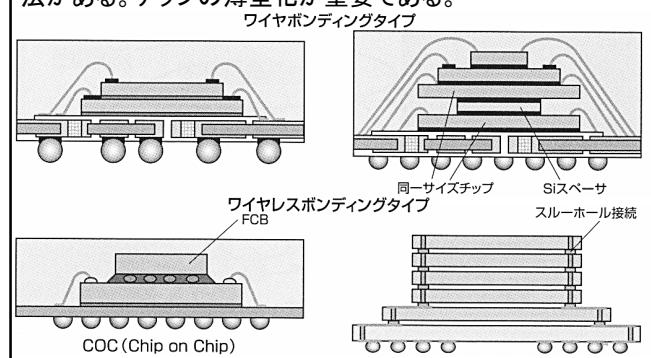

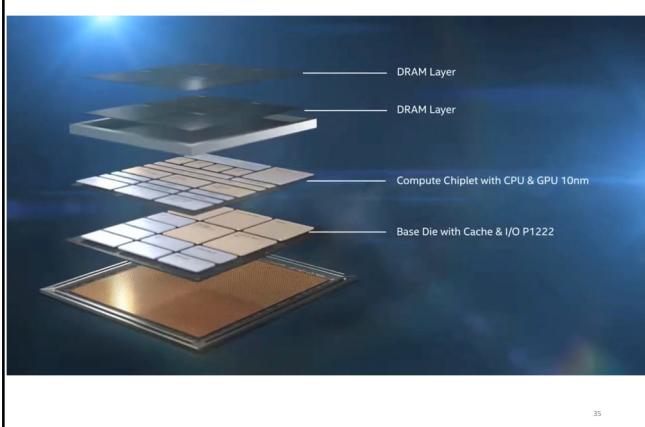

**3次元積層チップ:** 複数チップを積層させて実装面積効率を上げつつ、部品間の配線長を短縮する。ボンディングを使う方法とSi貫通電極(TSV: Through-Silicon Via)を使う方法がある。チップの薄型化が重要である。

## Intel Foveros:

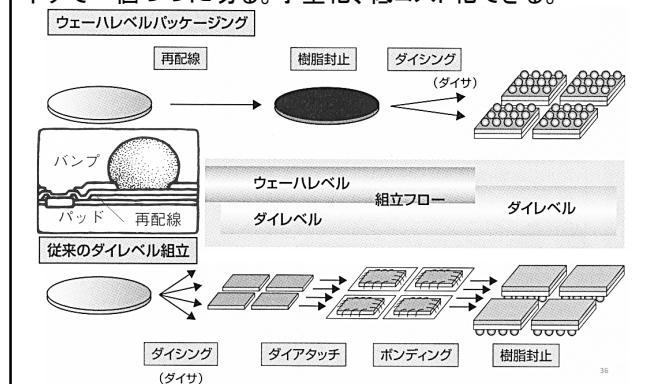

**ウェハーレベルパッケージング:** ウエハー状態で再配線、樹脂封止、ハンダバンプ外部端子形成まで行った後に、ダイサで一個づつに切る。小型化、低コスト化できる。

**次回の予告:** 素子分離、モノリシック受動素子

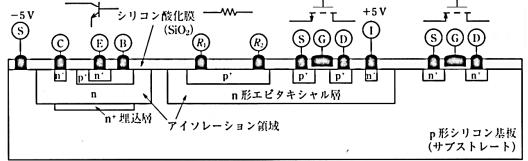

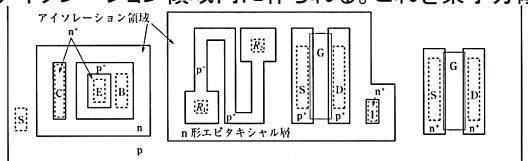

Si基板内の各電子素子は、互いに電気的に分離絶縁されなければならない。そのために基板と電気的に絶縁されたアイソレーション領域内に作られる。これを素子分離といふ。

(a) パーク

(b) 抵抗

(c) p-MOS

(d) n-MOS

37

シリコン酸化膜 (SiO<sub>2</sub>)

n 形エピタキシャル層

p 形シリコン基板 (サブストレート)

n+埋込み

アイソレーション領域

37