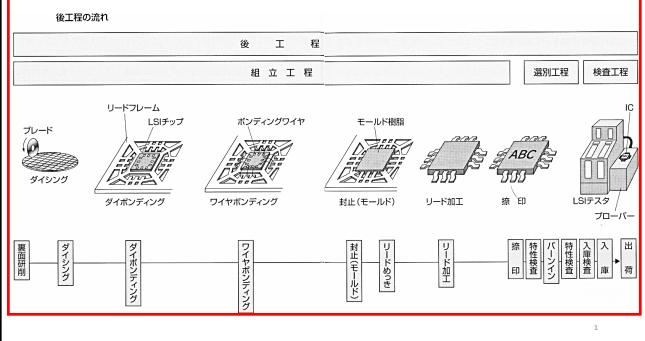

## 前回の復習: 後工程:

前工程でSiウェハー上に電子回路を製造した後に、後工程で一個づつの製品にする。

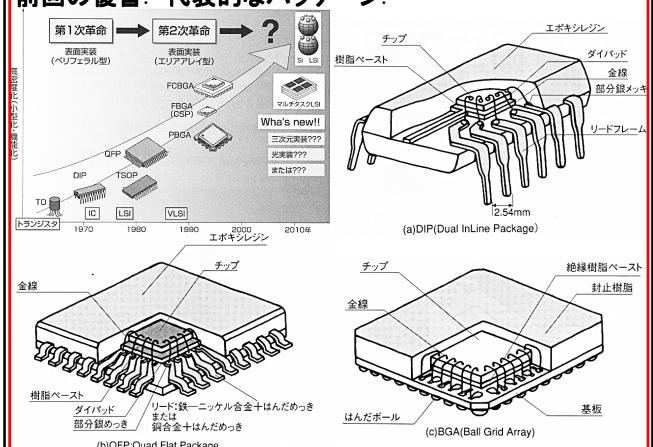

## 前回の復習: 代表的なパッケージ:

## 前回の復習: Multi-Chip Module:

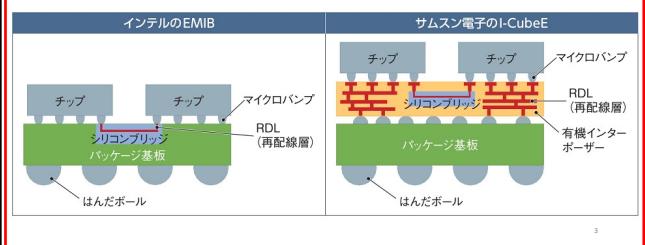

複数のICチップをパッケージに封止して一つのICにする。プリント基板を通してパッケージ内でインターポーラーを介して配線することで信号の伝達遅れを最小限にして、システムを高速化・コンパクト化できる。

Embedded Multi-die Interconnect Bridge (EMIB)

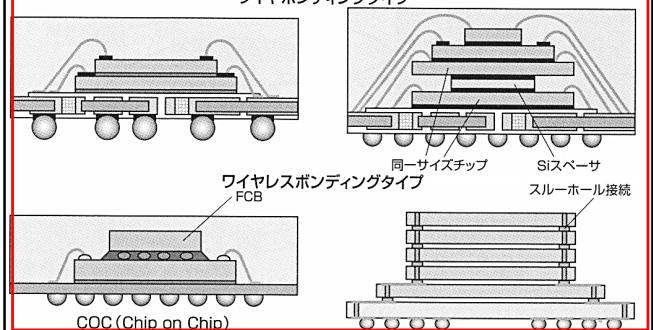

前回の復習: 3次元積層チップ: 複数チップを積層させて実装面積効率を上げつつ、部品間の配線長を短縮する。ボンディングを使う方法とSi貫通電極(TSV: Through-Silicon Via)を使う方法がある。チップの薄型化が重要である。

ワイヤボンディングタイプ

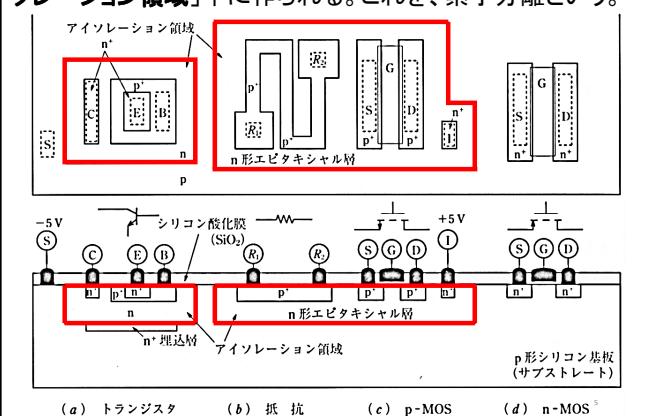

素子分離: 集積回路の各素子は、互いに絶縁された「アイソレーション領域」中に作られる。これを、素子分離という。

## 素子分離の種類:

「アイソレーション領域」の作製方法には、主に以下の様な方法がある。

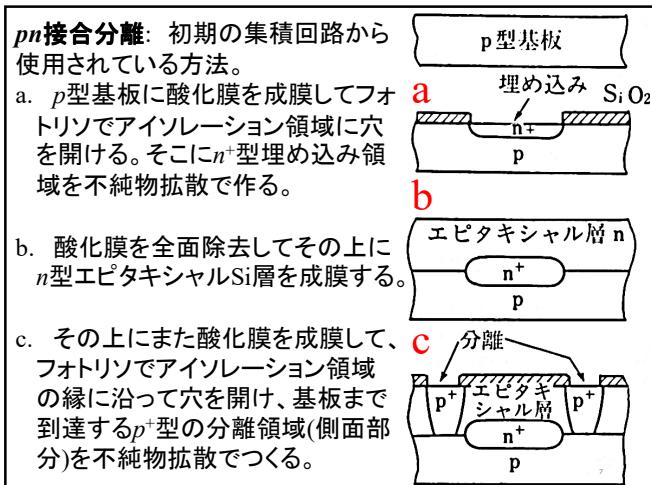

1. *pn接合分離*: *pn*接合に逆バイアスかけて絶縁する。

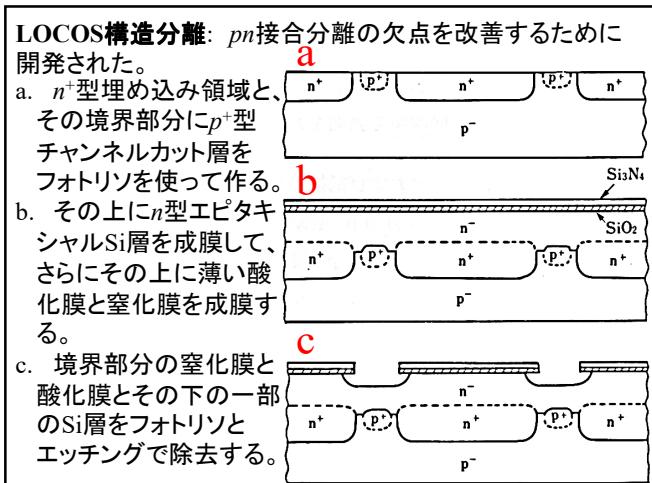

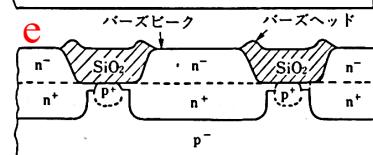

2. *LOCOS*(Local Oxidation of Silicon)構造分離: 局所的に熱酸化膜を成長させて絶縁する。

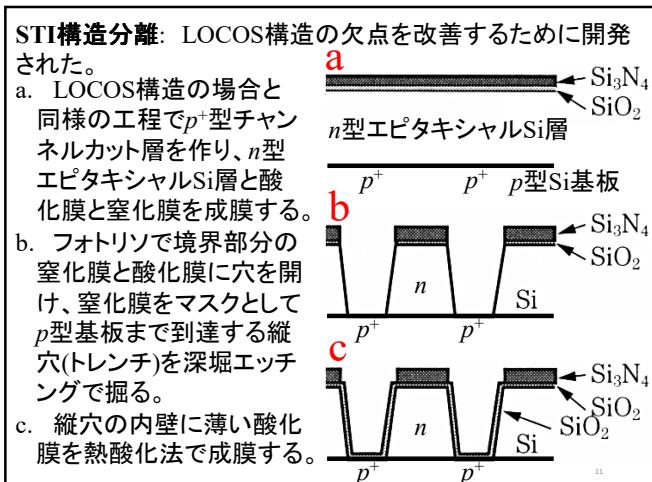

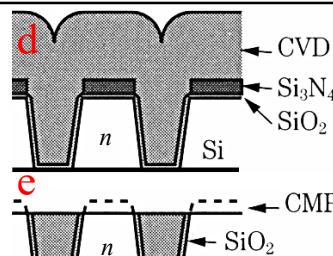

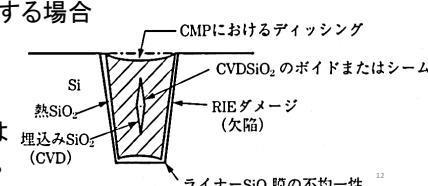

3. *STI*(Shallow Trench Isolation)構造分離: Si基板に深い溝を掘り、そこにCVDで酸化シリコンを詰め込んで絶縁する。

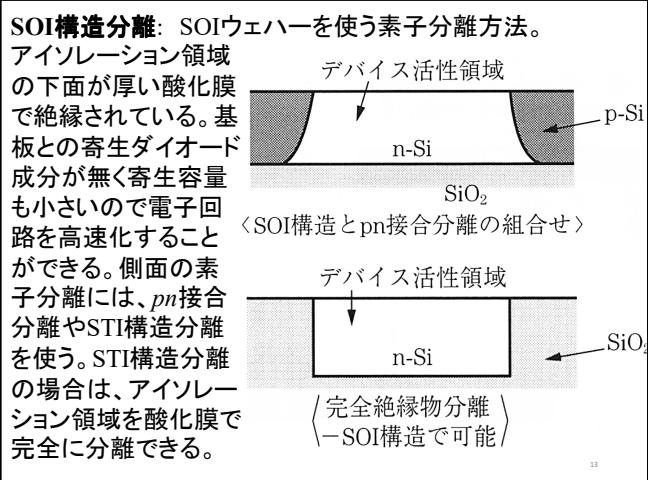

4. *SOI*(Silicon On Insulator)構造分離: SOI基板を使って絶縁する。

これで、p型で囲まれたn型のSi領域ができる。これがアイソレーション領域となる。

p型Si基板を電子回路の最低電位(ユニポーラならグランド電位、バイポーラなら-Vcc)に接続しておけば、アイソレーション領域を囲っているpn接合には必ず逆バイアス電圧がかかるので、各アイソレーション領域と基板の間には電流が流れず素子分離をすることができる。

しかし、pn接合分離には、基板との間の寄生容量(ダイオードのコンデンサ作用)が大きいという欠点や、小型化し難いという欠点がある。

(補足) n<sup>+</sup>埋め込み層が要らない場合には、p型Si基板にドナー不純物を入れてn型のアイソレーション領域にする簡単な方法もある。

8

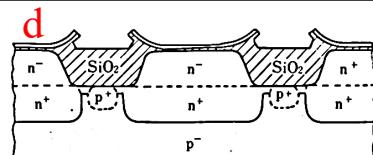

d. 窒化膜をマスクとして、厚い分離酸化膜を熱酸化法で成膜する。

e. 窒化膜と薄い酸化膜をエッティングで取り除いてアイソレーション領域が完成する。

分離酸化膜の幅は、pn接合分離のp<sup>+</sup>型分離領域より狭くできるので、集積度を上げられる。しかし、分離酸化膜にバースヘッドやバースピークができると、素子形状が歪む。

(補足) LOCOS構造分離でもアイソレーション領域の下面是pn接合分離である。

10

d. CVD法で縦穴の中にSiO<sub>2</sub>を埋め込む。これをトレンチ埋め込みという。

e. CMP法で表面を研磨して窒化膜と酸化膜を除去しつつ、表面を平坦にしてアイソレーション領域が完成する。

(トレンチ埋め込みやCMPの工程で欠陥が発生する場合もある。)

(補足) アイソレーション領域の下面是pn接合分離である。

12

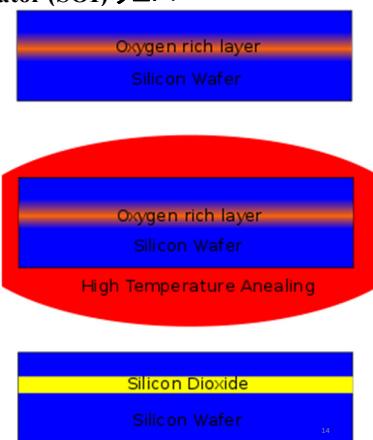

### (補足) Silicon on Insulator (SOI)ウェハー

Si内部に $\text{SiO}_2$ の絶縁膜を形成したウェハー。主流の製造方法であるSIMOX法では、ウェハー内部に酸素をイオン注入し熱処理して酸化膜をSi内部に形成する。

高速化・低消費電力化に適しているので、パワー半導体やアナログ半導体で良く使用される。

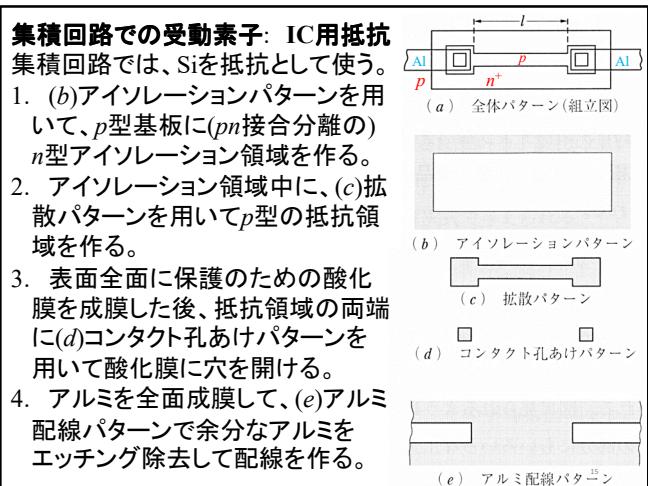

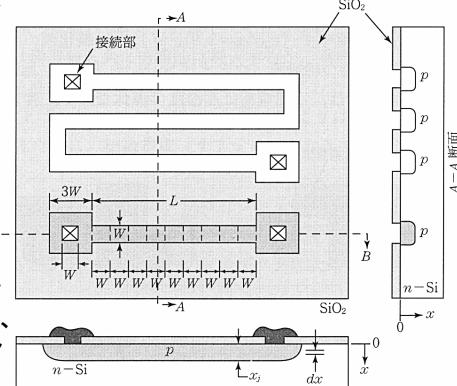

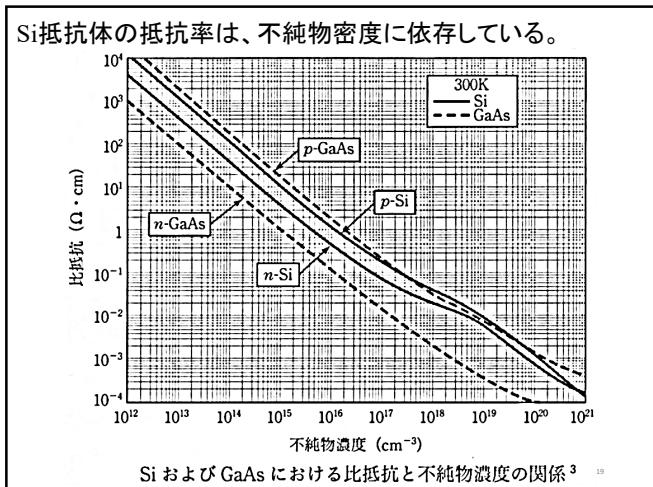

### 集積回路用Si抵抗の抵抗値:

長さが $L$ 、幅が $W$ である*p*型抵抗の値を計算してみよう。深さ方向に $x$ 軸を取り、厚さ $dx$ の微小薄層を考える。

この微小薄層の電気伝導度 $\sigma(x)$ を $\sigma(x)$ 、断面積を $S(=Wdx)$ とすると、微小コンダクタンス $dG$ (電気抵抗の逆数)は、

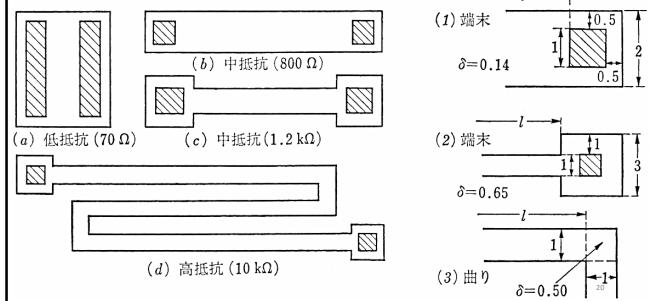

IC用抵抗。各部の寸法は $W$ で、電極も同寸法。

$$dG = \frac{\sigma(x)S}{L} = \frac{\sigma(x)W}{L} dx,$$

となる。また、素電荷 $e$ 、ホール移動度 $\mu_p$ 、ホール密度 $p(x)$ を用いると、 $\sigma(x) = e\mu_p p(x)$ と表せるので、

$$dG = \frac{e\mu_p p(x)W}{L} dx,$$

となる。この $dG$ を $pn$ 接合深さ $x_j$ まで積分すれば、Si抵抗体のコンダクタンス $G$ となるので、

$$G = \left( e \int_0^{x_j} \mu_p p(x) dx \right) \frac{W}{L} \equiv \frac{W}{\rho_s L},$$

となる。ここで $\rho_s$ はシート抵抗である。

2段階不純物拡散後のホール密度 $p(x)$ は一般的に複雑な分布をしており、かつホール移動度 $\mu_p$ もホール密度 $p(x)$ に依存しているので、この積分は簡単には実行できない。 $\rho_s$ を求めるには計算機シミュレーションか、実測する。

また、電気抵抗 $R$ はコンダクタンス $G$ の逆数で、

$$R = \frac{1}{G} = \frac{\rho_s L}{W}, \quad (12.1)$$

となる。一般にシート抵抗 $\rho_s$ の値はトランジスタのベース設計から決まっており、 $\rho_s = 30 \sim 800 \ [\Omega/\square]$ 程度である。

注) 電気抵抗の作製工程はトランジスタのベース形成プロセス(後述)等と一緒に行われることが多い。

抵抗の長さ $L$ と幅 $W$ の比を整数 $n$ にすると( $L=nW$ )、(12.1)式から $R=\rho_s L/W=n\rho_s$ となり抵抗 $R$ の値は $\rho_s$ の $n$ 倍になる。しかし、一般には末端や曲がり部分のシート抵抗は直線部分とある係数 $\delta$ だけ)異なっているのでその部分の補正が必要である。つまり、直線抵抗では $R=\rho_s(L/W+2\delta)=(n+2\delta)\rho_s$ となる。

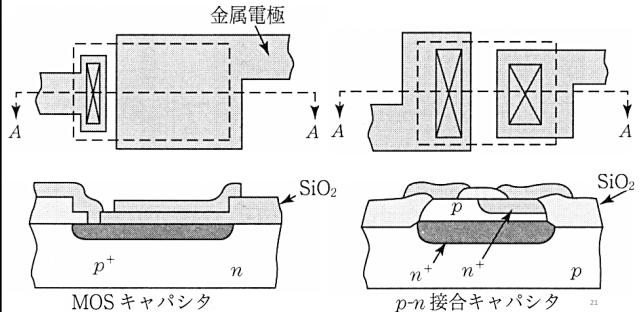

**集積回路用コンデンサ**: 集積回路では、MOS構造とpn接合構造のコンデンサが使われる。両構造とも、集積回路上では占有面積SIは大きくできず、誘電層の厚さdもあまり薄くないので、静電容量C( $=\epsilon S/d$ )は大きくできない。通常のIC用コンデンサの静電容量は0.1~50 pF程度である。

*pn*接合のコンデンサ:

*pn*接合は逆バイアスをかけると空乏層が広がりコンデンサとして機能する。素電荷を $e$ 、誘電率を $\epsilon_s$ 、内蔵電位を $V_{bi}$ 、ドナー・アクセプター密度を $N_d, N_a$ とすると、単位面積当たりの静電容量 $C$ は、

$$C = \sqrt{\frac{e\varepsilon_s N_d N_a}{2(N_d + N_a)(V_{bi} - V)}},$$

となり、バイアス電圧  $V$  に依存する。 $C$  を大きくするためには、不純物密度  $N_d, N_a$  を増やせば良いが、耐電圧が低くなってしまう。さらに、一般的に不純物密度はトランジスタ設計の方で既に決まっているので変えられないことが多い。

また、 $pn$ 接合のコンデンサでは、 $pn$ 接合部分の比抵抗が高いため、MOS構造のコンデンサよりも直列寄生抵抗が大きい。

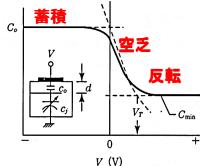

**MOS構造のコンデンサ:** 酸化膜による静電容量 $C_0$ と半導体下部電極の空乏領域による静電容量 $C_j$ を直列につないだものが、全体の静電容量 $C$ となる。このうち $C_j$ の方は一般にバイアス電圧 $V$ に依存していて、

$$C = \frac{\varepsilon_{ox}}{d_s \sqrt{1 + 2\varepsilon_{ox}^2 V / e N_a \varepsilon_s d^2}},$$

となる(付録1参照)。しかし、下部電極を高濃度にドープすることで直列寄生抵抗値を小さくしつつ空乏領域の発生を抑えて、バイアス依存性を減らすことができる。さらに、 $C_0$ を上げるために、酸化膜の代わりに高誘電率材料を使うこともある。

## モノリシック・コンデンサに用いられる誘電体材料の特性

|                   | シリコン酸化膜<br>(MOS 容量)     | シリコン空乏層<br>(pn 接合容量)    | シリコン窒化膜<br>(MOS 容量)      |

|-------------------|-------------------------|-------------------------|--------------------------|

| 比誘電率 $\epsilon_r$ | $\approx 3.9$           | $\approx 12$            | $\approx 7.5$            |

| 臨界電界 $E_c$ [V/cm] | $\approx 6 \times 10^6$ | $\approx 3 \times 10^5$ | $\approx 10 \times 10^6$ |

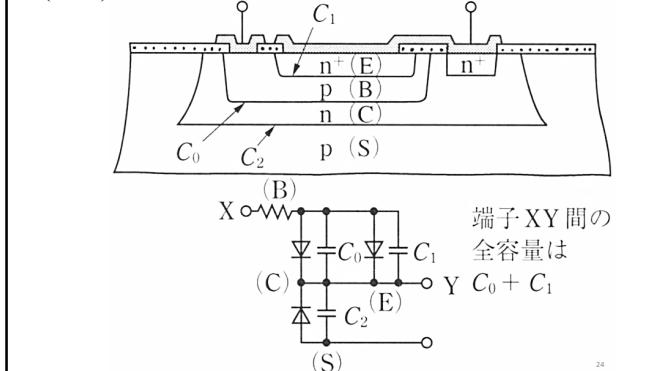

*pn*接合のコンデンサの例: バイポーラトランジスタのベースをX端子(負極)とし、エミッタとコレクタを短絡したものをY端子(正極)とする。 X Y

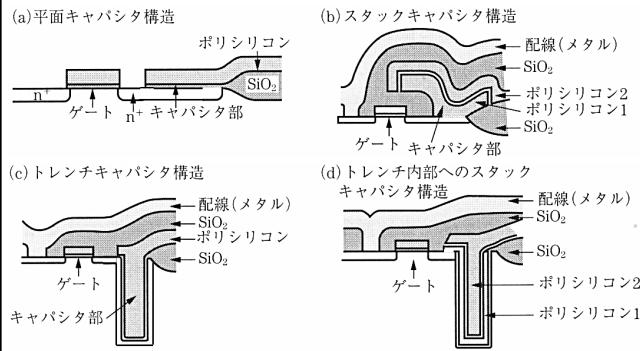

**DRAM用のコンデンサ:** DRAMのメモリセルはMOS-FETとコンデンサ各1個づつから構成されている。MOS-FETの微細化に合わせて、コンデンサも微細化したが、表面積と静電容量を確保するために3次元立体化が進んだ。

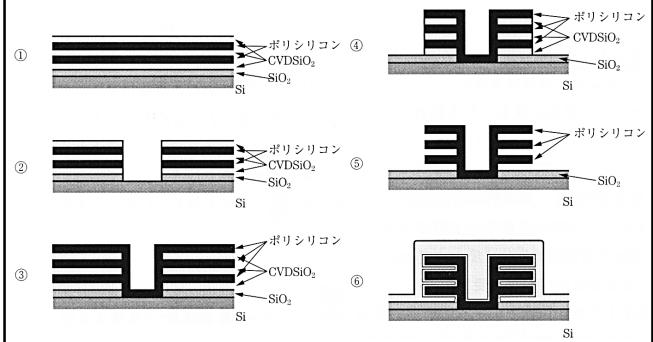

**フィン型3次元キャパシタの製造工程:** ①ポリシリコンとSiO<sub>2</sub>の積層膜、②パターン・エッチング、③ポリシリコン成膜、④パターン・エッチング、⑤SiO<sub>2</sub>ウェットエッチング、⑥誘電膜形成+ポリシリコン電極形成

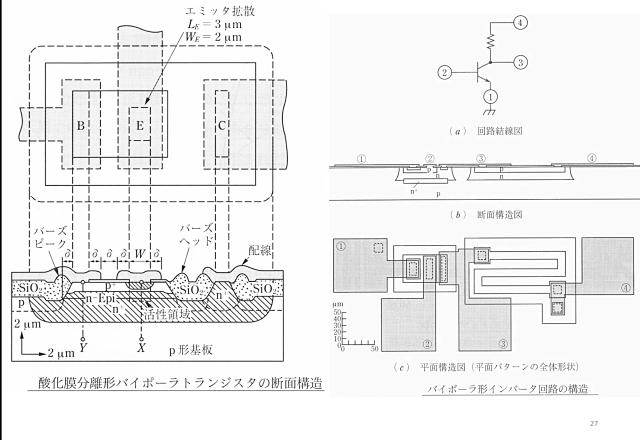

**次回の予告: バイポーラIC、**

**(付録1) MOS構造の静電容量:**

MOS構造の静電容量は、酸化膜によるもの $C_0$ と半導体の空乏領域によるもの $C_j$ を直列につないだものになる。単位面積当たりの $C_0$ は平行平板のコンデンサーの公式から、 $C_0 = \epsilon_{ox} / d$ , ( $\epsilon_{ox}$ :酸化膜の誘電率,  $d$ :酸化膜の厚さ)となる。

また、 $C_j$ の方はバイアス電圧に依存している。 $pn$ 接合の静電容量の式から、バイアス $V < 0$ (蓄積状態)の時は $C_j = 0$ となるので、 $C = C_0$ となる。

しかし、 $V > 0$ (空乏状態)の時は、

$C_j = \epsilon_s / w$ , ( $\epsilon_s$ :半導体の誘電率,  $w$ :空乏領域の幅)となる。ここで、(付録2)の空乏領域の幅 $w$ を表面電位 $\Psi_s$ からバイアス $V$ の関数になおすと、

27

28

$$\begin{aligned}

w &= \sqrt{\frac{2\epsilon_s \Psi_s}{eN_a}} = \sqrt{\frac{2\epsilon_s (V - V_{ox})}{eN_a}} = \sqrt{\frac{2\epsilon_s (V - Q_s / C_0)}{eN_a}} \\

&= \sqrt{\frac{2\epsilon_s (V - eW_{n_a} / C_0)}{eN_a}}, \quad \left( Q_s = ewN_a : \text{半導体表面} \right. \\

&\quad \left. \text{電荷密度} \right) \\

eN_a w^2 &= 2\epsilon_s (V - eW_{n_a} / C_0), \\

eC_0 N_a w^2 + 2\epsilon_s eN_a w - 2\epsilon_s C_0 V &= 0, \\

w &= \left\{ \epsilon_s eN_a \pm \sqrt{(\epsilon_s eN_a)^2 + 2e\epsilon_s C_0^2 N_a V} \right\} / eC_0 N_a \\

&= \frac{-\epsilon_s}{C_0} + \sqrt{\frac{eN_a \epsilon_s^2 + 2\epsilon_s C_0^2 V}{eN_a C_0^2}},

\end{aligned}$$

となるので、空乏領域による静電容量 $C_j$ は、

30

$$\begin{aligned}

C_j &= \frac{\epsilon_s}{w} = \epsilon_s \left/ \left( \frac{-\epsilon_s}{C_0} + \sqrt{\frac{eN_a \epsilon_s^2 + 2\epsilon_s C_0^2 V}{eN_a C_0^2}} \right) \right. \\

&= \left( \frac{-1}{C_0} + \sqrt{\frac{1}{C_0^2} + \frac{2V}{eN_a \epsilon_s}} \right)^{-1}, \quad \left( C_0 = \frac{\epsilon_{ox}}{d} \right) \\

\text{となる。従って、MOS構造全体の静電容量} C \text{は、} \\

C &= \left( \frac{1}{C_0} + \frac{1}{C_j} \right)^{-1} = \frac{C_0 C_j}{C_0 + C_j} = \frac{C_0}{1 + C_0 / C_j} \left( = \frac{C_0}{1 + \epsilon_{ox} w_m / \epsilon_s d} \right) \\

&= C_0 \left/ \left\{ 1 + C_0 \left( \frac{-1}{C_0} + \sqrt{\frac{1}{C_0^2} + \frac{2V}{eN_a \epsilon_s}} \right) \right\} \right\} = \left( \frac{1}{C_0} + \frac{2V}{eN_a \epsilon_s} \right)^{-\frac{1}{2}} \\

&= C_0 \left/ \sqrt{1 + \frac{2C_0^2 V}{eN_a \epsilon_s}} = \epsilon_{ox} \left/ d \sqrt{1 + \frac{2\epsilon_{ox}^2 V}{eN_a \epsilon_s d^2}} \right. \right\}, \quad \text{となる。}

\end{aligned}$$

31

$$C = \epsilon_{ox} \sqrt{d \left( 1 + \frac{2\epsilon_{ox}^2 V}{eN_a \epsilon_s d^2} \right)},$$

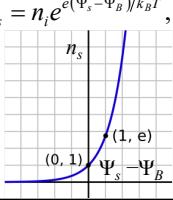

始めは、バイアス電圧  $V$  を上げると静電容量  $C$  は減少する。しかし、バイアス電圧  $V$  をさらに増加させて、表面電位が  $\Psi_s > \Psi_B$  になると反転状態が始まり、 $\Psi_s = 2\Psi_B$  になると表面電子密度  $n_s$  がアクセプター密度  $N_a$  とほぼ同じになり、界面近傍で半導体の極性が  $p$  型から  $n$  型に変わり反転状態となる。この時、空乏領域幅が最大の  $w_m$  となり、静電容量が最少の  $C_{min}$  となる。

それ以降は  $V$  を上げて表面電子密度  $n_s$  を増やしても、 $n_s$  と表面電位  $\Psi_s$  との関係が右記の指數関数となっているため、 $\Psi_s$  はほとんど増加せず、同様に  $w$  もほとんど増加しない。従って、 $C$  も減少しなくなる。

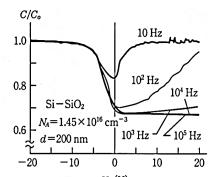

(a) 高周波 MOS C-V 曲線とそれを近似する部分図(点線)。挿入図は容量が直列に接続されていること示している。(b) C-V 曲線の測定周波数依存性<sup>2</sup>。

(注意)上記の反転領域での静電容量の説明は、測定信号が高周波( $>100\text{Hz}$ )の場合のみ正しい。低周波になると反転状態の電荷が信号周波数で変化するようになり  $C=0$  となる。従って、低周波の反転状態では  $C \approx C_0$  となる。

Si-SiO<sub>2</sub>,  $N_d = 1.45 \times 10^{13} \text{ cm}^{-3}$ ,  $d = 200 \text{ nm}$

この時の  $w_m$  と  $C_{min}$  は、

$$w_m = \sqrt{\frac{2\epsilon_s \Psi_s}{eN_a}} \cong \sqrt{\frac{4\epsilon_s \Psi_B}{eN_a}},$$

$$C_{min} = \frac{C_0}{1 + \epsilon_{ox} w_m / \epsilon_s d} = \frac{\epsilon_{ox}}{d + w_m \epsilon_{ox} / \epsilon_s},$$

となる。以上をまとめると、

$$C = \begin{cases} C_0, & (V < 0, \text{蓄積状態}) \\ \frac{\epsilon_{ox}}{d\sqrt{1 + 2\epsilon_{ox}^2 V / eN_a \epsilon_s d^2}}, & (V_T > V > 0, \text{空乏状態}) \\ \frac{\epsilon_{ox}}{(d + w_m \epsilon_{ox} / \epsilon_s)}, & (V > V_T, \text{反転状態}) \end{cases}$$

( $V_T$ : 閾値電圧) となる。蓄積状態と反転状態では静電容量  $C$  は一定で、空乏状態ではバイアス電圧  $V$  が増えると、 $C$  は減少する。

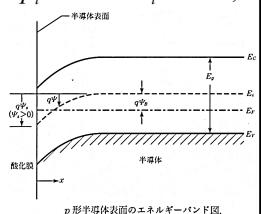

各界面状態での  $\Psi_s$  と  $\Psi_B$  の大小関係を示すと、

- $\Psi_s < 0$ : 蓄積状態、( $n_s \ll p_s$ )

- $\Psi_s = 0$ : フラットバンドの状態、( $n_s \approx p_s$ )

- $0 < \Psi_s < \Psi_B$ : 空乏状態、

- $\Psi_s = \Psi_B$ :  $n_s = p_s = n_i$ (真性キャリア密度)、

- $\Psi_s > \Psi_B$ : 反転状態 ( $n_s > p_s$ )

となる。

表面から内部に向かっての電位  $\Psi(x)$  の変化を求めるために、1次元のポアソン方程式を解くと、

$$\frac{d^2 \Psi}{dx^2} = -\frac{\rho(x)}{\epsilon_s}, \quad \rho(x) = \begin{cases} -eN_a, & (0 \leq x \leq w) \\ 0, & (w < x) \end{cases},$$

( $N_a$ : アクセプター密度,  $w$ : 空乏領域の幅)

$$\Psi = \begin{cases} \frac{eN_a}{2\epsilon_s} x^2 + Ax + B, & (0 \leq x \leq w) \\ 0, & (w < x) \end{cases}, \quad (A, B: \text{積分定数})$$

36

## (付録2) 表面空乏領域:

半導体の表面電位  $\Psi_s$  は、金属電極にかけたバイアス電圧  $V$  から酸化膜にかかる電圧  $V_{ox}$  を引いた値( $\Psi_s = V - V_{ox}$ )になる。また、以前の結果から半導体表面での電子とホール密度  $n_s, p_s$  は、

$$n_s = N_C e^{-\frac{E_C - E_f}{k_B T}} = N_C e^{-\frac{E_C - E_i}{k_B T}} e^{-\frac{E_i - E_f}{k_B T}} = n_i e^{-\frac{E_i - E_f}{k_B T}} = n_i e^{-\frac{\Psi_s - \Psi_B}{k_B T}},$$

$$p_s = N_V e^{-\frac{E_f - E_V}{k_B T}} = N_V e^{-\frac{E_i - E_V}{k_B T}} e^{-\frac{E_f - E_i}{k_B T}} = p_i e^{-\frac{E_f - E_i}{k_B T}} = p_i e^{-\frac{\Psi_B - \Psi_s}{k_B T}},$$

( $E_i$ : 真性フェルミエネルギー,)

$n_i = p_i$ : 真性キャリア密度,

$\Psi_B$ : 半導体内部での  $E_i - E_f$ )

となる。

となる。境界条件は  $\Psi(0) = \Psi_s$ 、 $\Psi(w) = d\Psi(x)/dx|_{x=w} = 0$  ので、これを用いて積分定数  $A, B$  を求める。  $(\Psi(x) = eN_a x^2 / 2\epsilon_s + Ax + B)$

$$\Psi(0) = B = \Psi_s, \quad \left. \frac{d\Psi(x)}{dx} \right|_{x=w} = \frac{eN_a w}{\epsilon_s} + A = 0, \quad A = -\frac{eN_a w}{\epsilon_s},$$

$$\Psi(w) = \frac{eN_a w^2}{2\epsilon_s} - \frac{eN_a w^2}{\epsilon_s} + B = 0, \quad B = \frac{eN_a w^2}{2\epsilon_s} (= \Psi_s),$$

となり、最終的に、電位は、

$$\Psi(x) = \frac{eN_a}{2\epsilon_s} x^2 + Ax + B = \frac{eN_a x^2}{2\epsilon_s} - \frac{eN_a w x}{\epsilon_s} + \frac{eN_a w^2}{2\epsilon_s}$$

$$= \frac{eN_a}{2\epsilon_s} (x - w)^2 = \frac{eN_a w^2}{2\epsilon_s} \left(1 - \frac{x}{w}\right)^2 = \Psi_s \left(1 - \frac{x}{w}\right)^2,$$

となる。また、先程の  $\Psi_s$  を空乏領域の幅  $w$  について解くと、

37

$$\frac{eN_a w^2}{2\varepsilon_s} = \Psi_s, \quad w = \sqrt{\frac{2\varepsilon_s \Psi_s}{eN_a}},$$

となる。