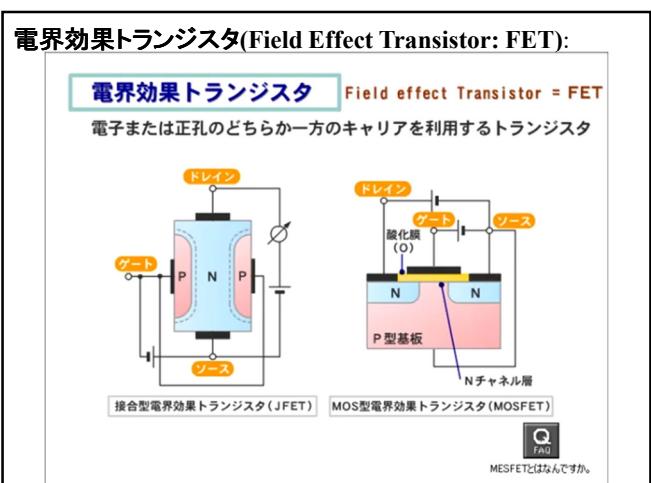

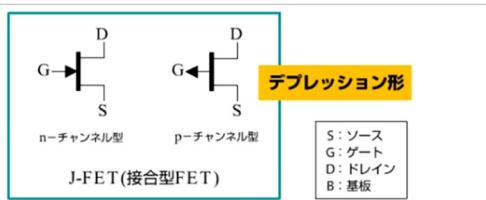

### FETの動作:

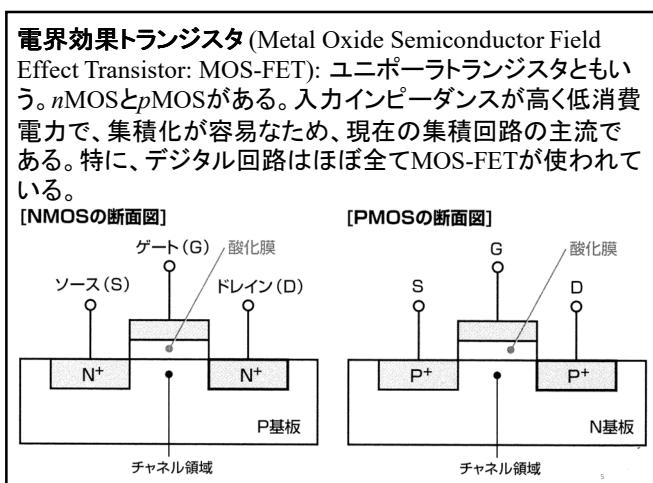

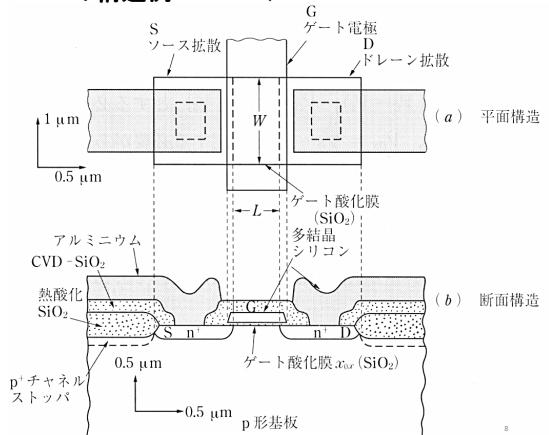

### MOS-FET ICの構造例: nMOS、

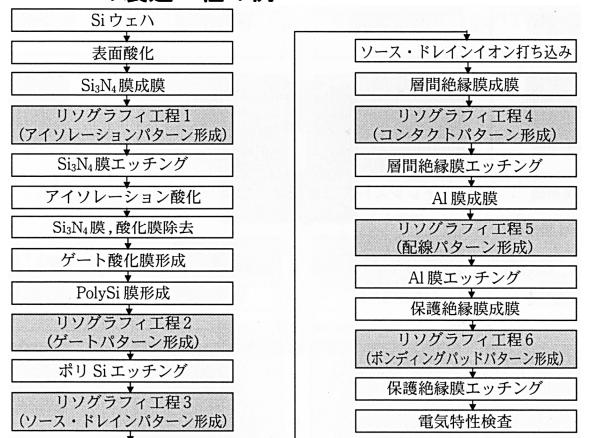

### MOS-FETの製造工程の例:

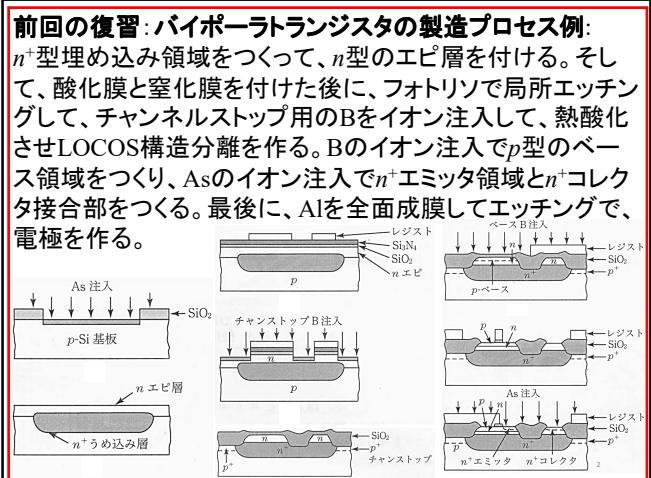

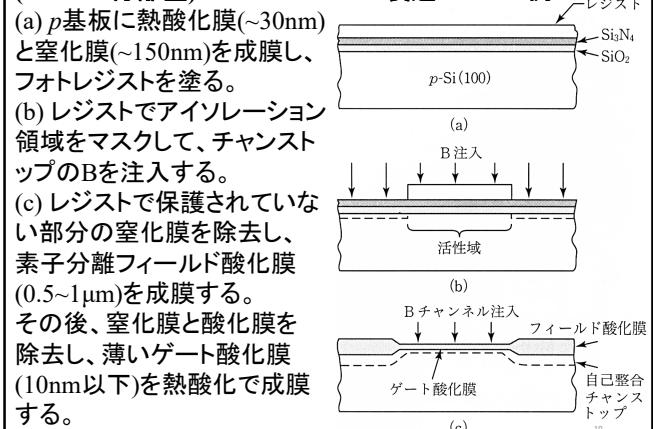

### (LOCOS分離型)nMOS-FET ICの製造プロセス例:

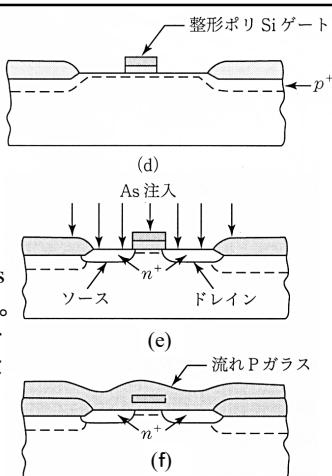

(d) ポリシリコン膜を全面に成膜して、ポリシリコン膜のシート抵抗を数十 [Ω/□] 程度に下げるためPをイオン注入する。その後、フォトリソでゲート電極部以外の余分な酸化膜とポリシリコン膜を除去する。

(e) ソースとドレイン部分にAsをイオン注入してn<sup>+</sup>型にする。

(f) 流れリンガラス(絶縁膜)を全面成膜して低温加熱し、なめらかな表面にする。

(g) フォトリソで電極部分のリンガラスをエッティング除去してコンタクトを形成し、アルミニウムを全面成膜する。その後、再びフォトリソで余分なアルミ部分をエッティング除去して、ソース、ゲート、ドレイン電極を作る。

## MOSの作製プロセスのまとめ:

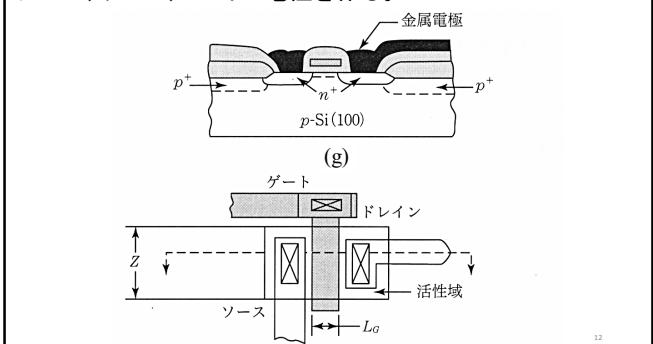

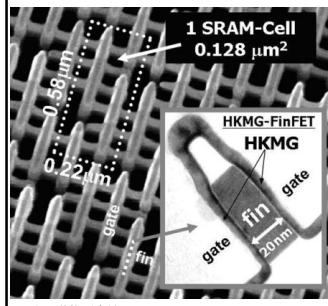

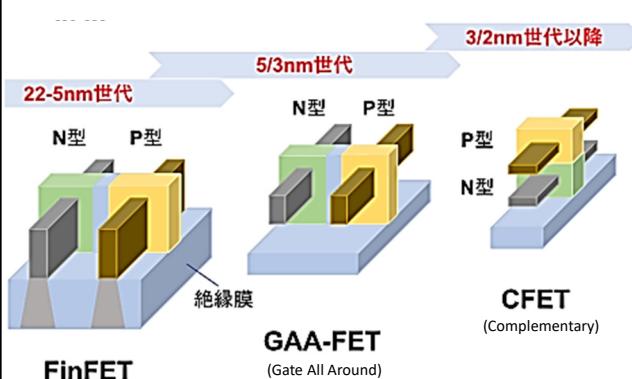

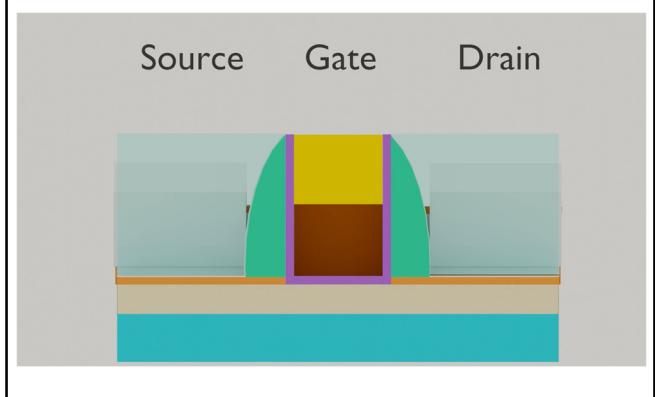

## マルチゲートFET:

ゲート構造を立体化してゲート面積を増やし、静電容量  $C_0$  を減らさずに素子サイズを縮小する。同時に、ゲート絶縁膜の膜厚を厚くしてリーク電流を抑制し低消費電力化する。

14

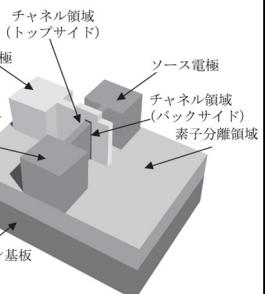

## マルチゲートFETの種類:

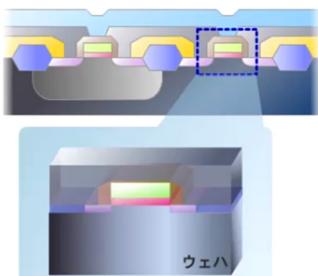

## マルチゲートFETの製造工程:

16

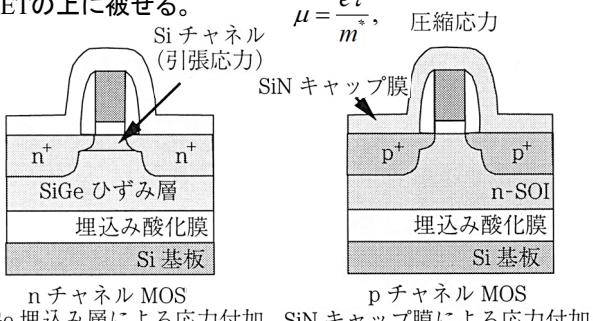

**歪みトランジスタ:** シリコンの格子間隔を広げる(縮める)と、電子(ホール)の有効質量  $m^*$  が小さくなり、FETの動作速度が数十%程度向上する。格子間隔を広げるにはチャネル下部に  $\text{Si}_{1-x}\text{Ge}_x$  ひずみ層をつくる。縮めるには  $\text{Si}_3\text{N}_4$  キャップ層をFETの上に被せる。

## 歪みシリコン模式図:

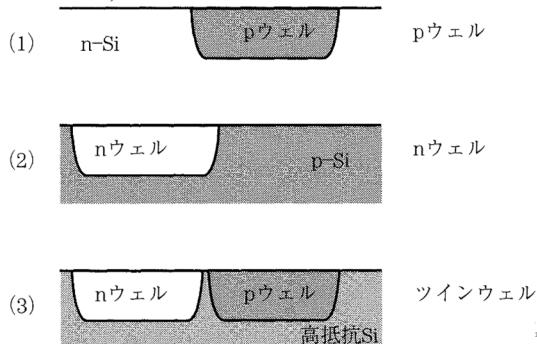

**集積回路のウェル領域:** CMOS(Complementary MOS)では、同一基板上にnMOSとpMOSの両方が作り込まれているため、ウェルという領域を形成して、その中にどちらか一方(または両方)の型のMOSをつくる。

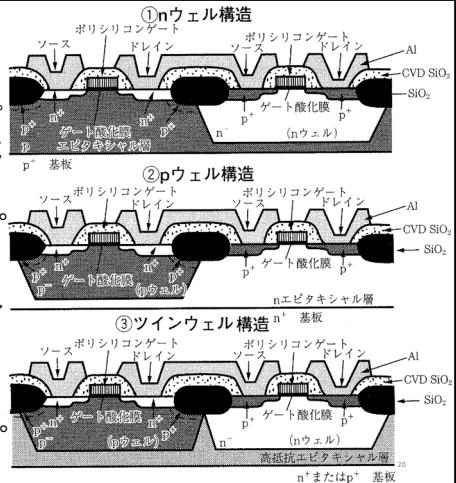

### 集積回路のCMOSの構造:

p(n)型Si基板の上にp(n)型のエピタキシャル層を成膜して、その中にn(p)ウェルを作る。ノンドープ(高抵抗)のエピタキシアル層を成膜した場合には両方のウェルを作る。n(p)ウェル内にp(n)MOSをつくる。

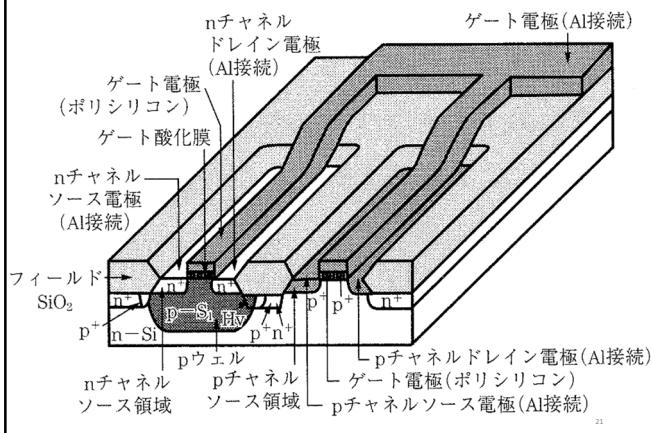

### pウェルのCMOSの構造例:

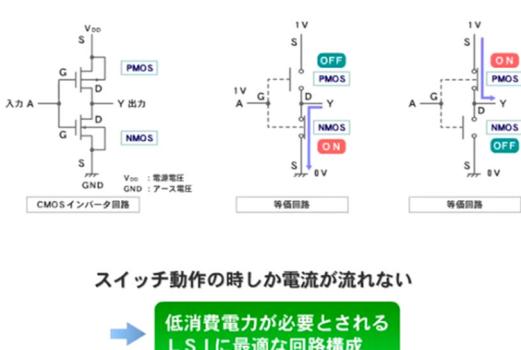

### CMOSの解説:

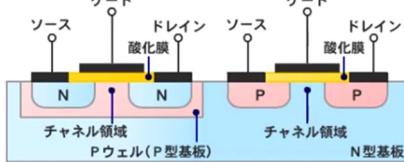

#### CMOS

NチャネルMOSとPチャネルMOSを組合せて回路を構成したデバイス

#### 特徴

- 消費電力が低い

- 低電圧でも動作する

- 半導体の中で、最も多く使用されている

### CMOSのNOT論理回路:

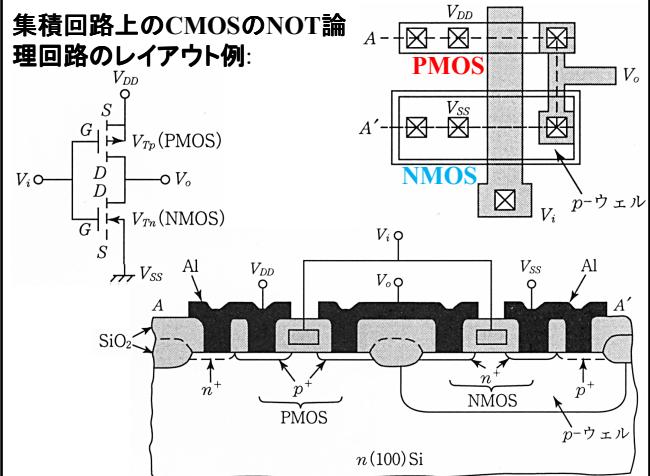

### 集積回路上のCMOSのNOT論理回路のレイアウト例:

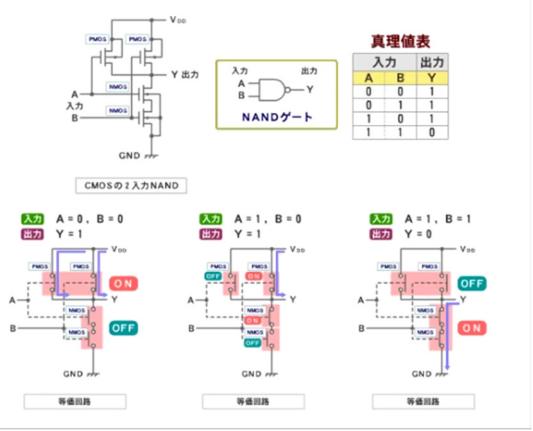

### NAND論理回路:

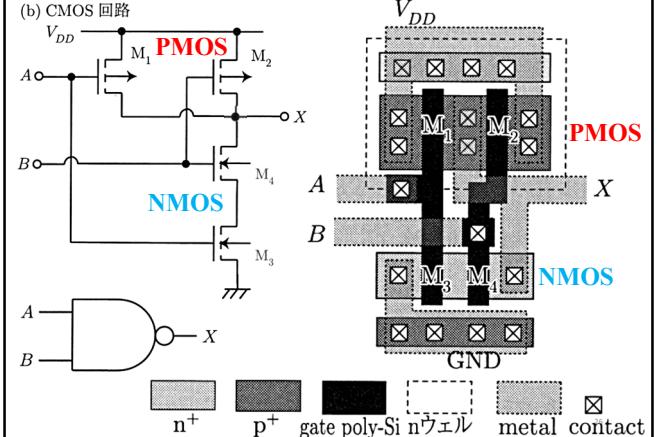

### CMOSのNAND論理回路のレイアウト例:

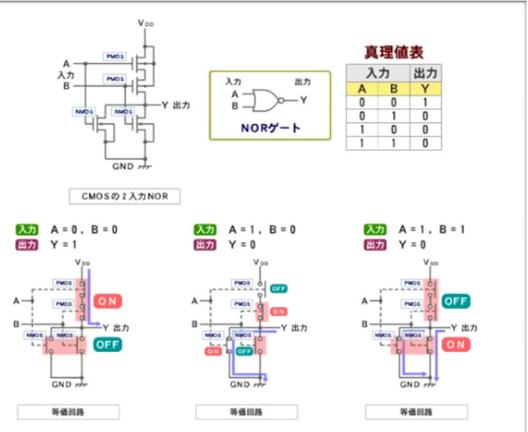

### NOR論理回路:

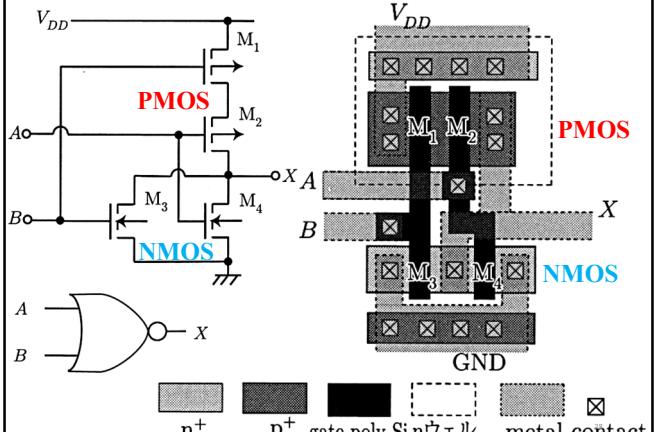

### CMOSのNOR論理回路のレイアウト例:

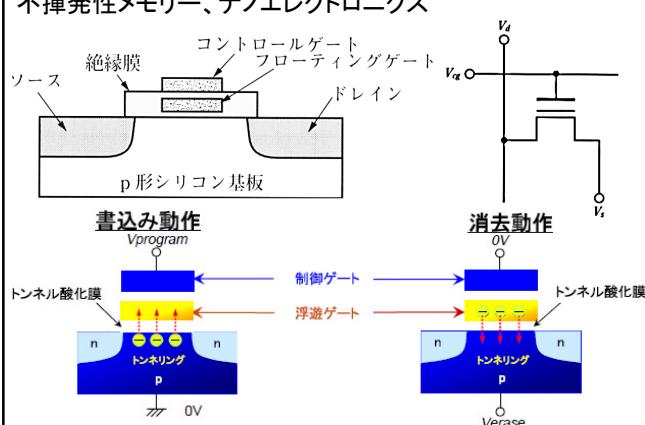

### 次回の予告: MOS-IC 2: 不揮発性メモリー、ナノエレクトロニクス